纳芯微全新推出集成化的Power Stage产品NSG65N15K,内部集成了高压半桥驱动器和两颗650V耐压的GaN开关管,可广泛适用于快充、储能、服务器电源等多种GaN应用场景。

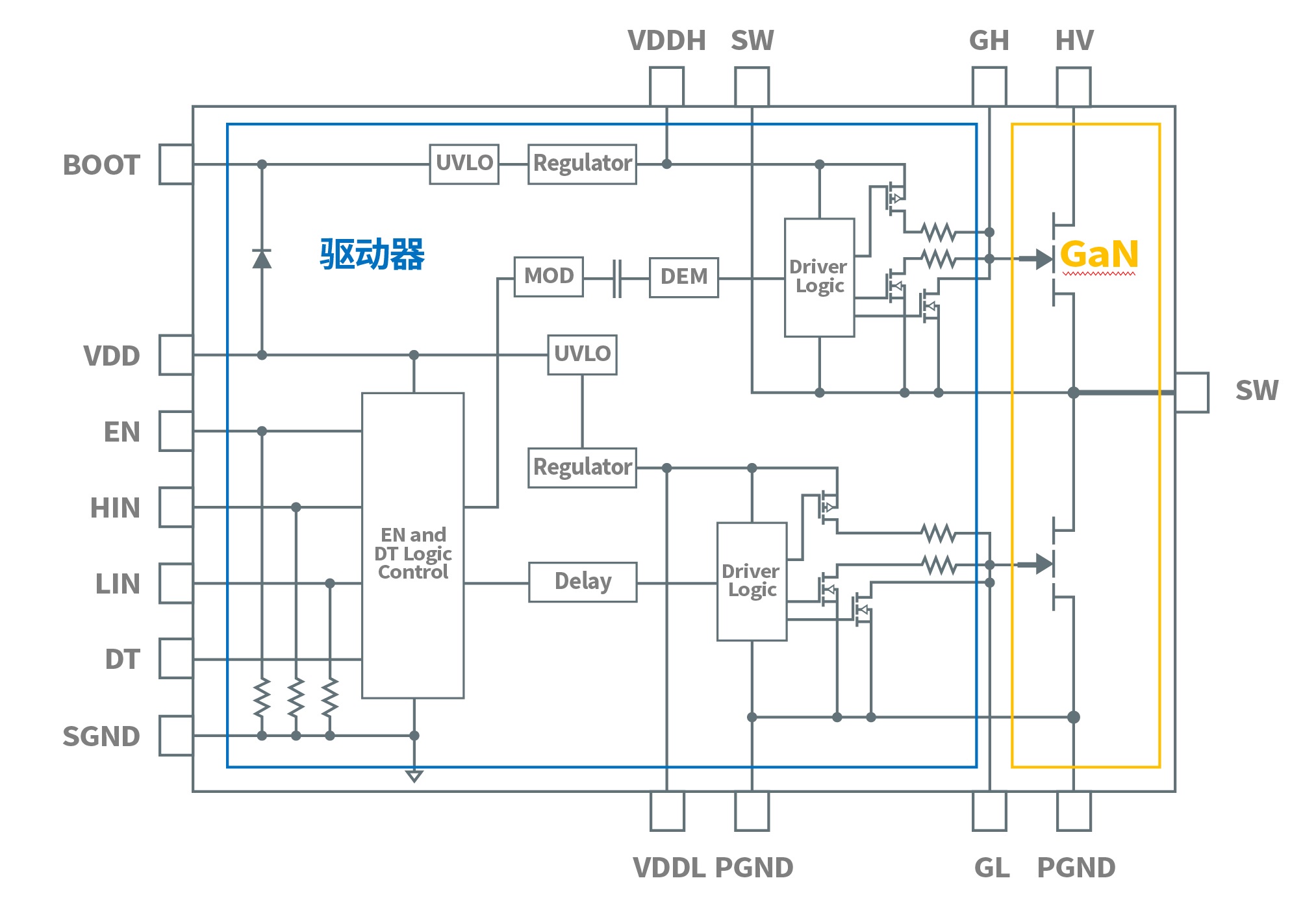

为进一步发挥GaN高频、高速的特性优势,纳芯微同时推出了集成化的Power Stage产品NSG65N15K,内部集成了半桥驱动器NSD2621和两颗耐压650V、导阻电阻150mΩ的GaN开关管,工作电流可达20A。NSG65N15K内部还集成了自举二极管,并且内置可调死区时间、欠压保护、过温保护功能,可以用于图腾柱PFC、ACF和LLC等半桥或全桥拓扑。

NSG65N15K功能框图

1. NSG65N15K用一颗器件取代驱动器和两颗开关管组成的半桥,有效减少元件数量和布板面积。

NSG65N15K是9*9mm的QFN封装,相比传统分立方案的两颗5*6mm DFN封装的GaN开关管加上一颗4*4mm QFN封装的高压半桥驱动,加上外围元件,总布板面积可以减小40%以上,从而有效提高电源的功率密度。同时,NSG65N15K的走线更方便PCB布局,有利于实现简洁快速的方案设计。

2. NSG65N15K的合封设计有助于减小驱动和开关管之间的寄生电感,简化系统设计并提高可靠性。

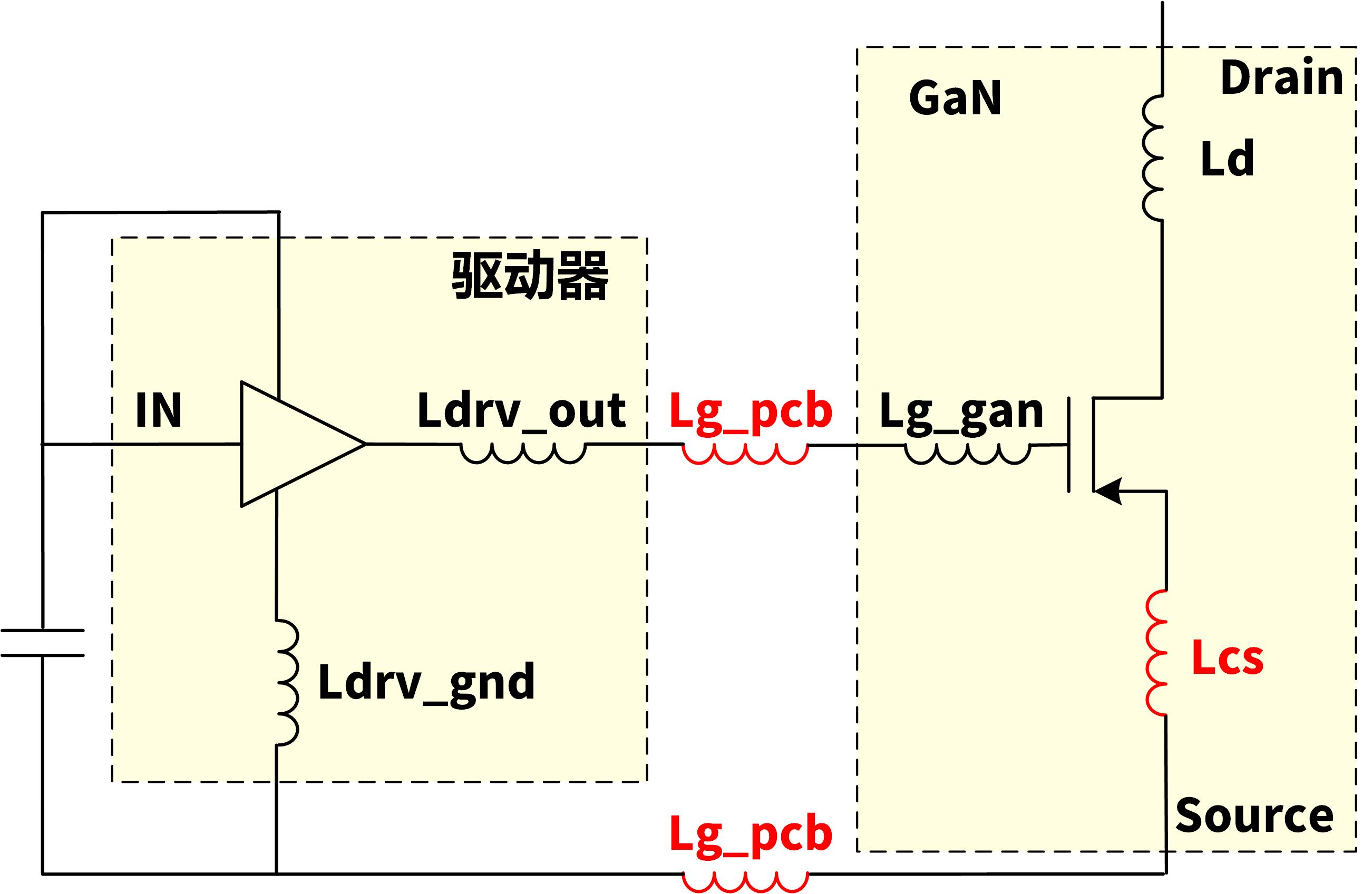

如下图所示,传统的分立器件方案,会引入由于PCB走线造成的栅极环路电感Lg_pcb和由于GaN内部打线造成的共源极电感Lcs。

传统分立方案引入寄生电感

其中,栅极环路电感Lg_pcb会在栅极电压开通或关断过程产生振铃,如果振铃超出GaN的栅源电压范围,容易造成栅极击穿;并且在上管开通过程中,高dv/dt产生的米勒电流会在下管的Lg_pcb上产生正向压降,有可能造成GaN的栅极电压大于开启电压,从而误导通。而共源极电感Lcs造成的影响,主要是会限制GaN电流的di/dt,增加额外的开关损耗;此外,在GaN开通过程电流增大,由于di/dt会在Lcs上产生正向压降,降低了GaN的实际栅极电压,增大了开通损耗。

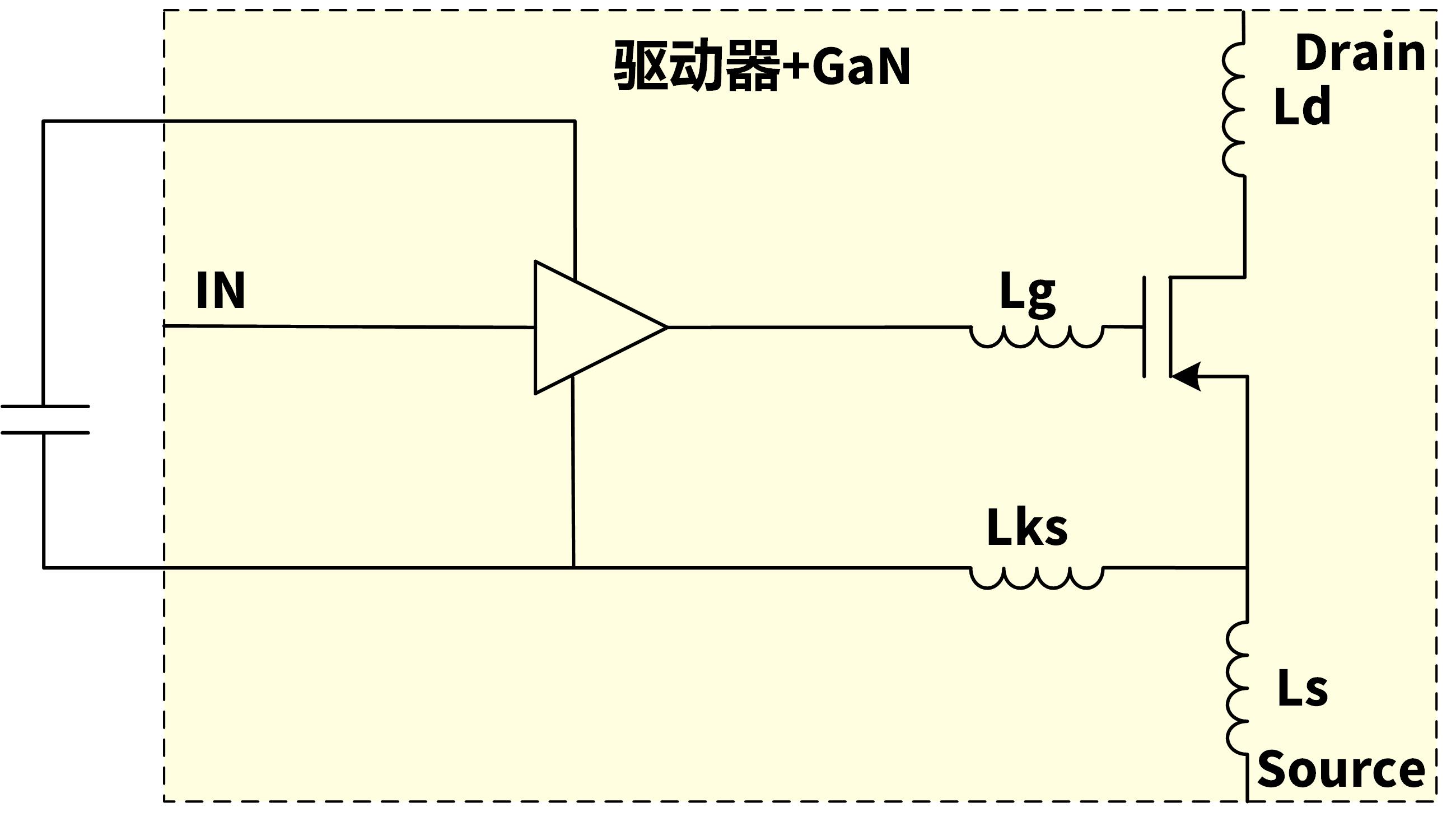

NSG65N15K减小杂散电感的影响

如上图所示,NSG65N15K通过将驱动器和GaN合封在一起,消除了共源极电感Lcs,并且将栅极回路电感Lg也降到最小,避免了杂散电感的影响,可以有效地提高系统效率与可靠性。